Tam SoC (System on Chip) quam SiP (System in Package) momenta magna in evolutione circuituum integratorum modernorum sunt, quae miniaturizationem, efficientiam, et integrationem systematum electronicorum permittunt.

1. Definitiones et Notiones Fundamentales SoC et SiP

SoC (Systema in Chip) - Totius systematis integratio in unum chip

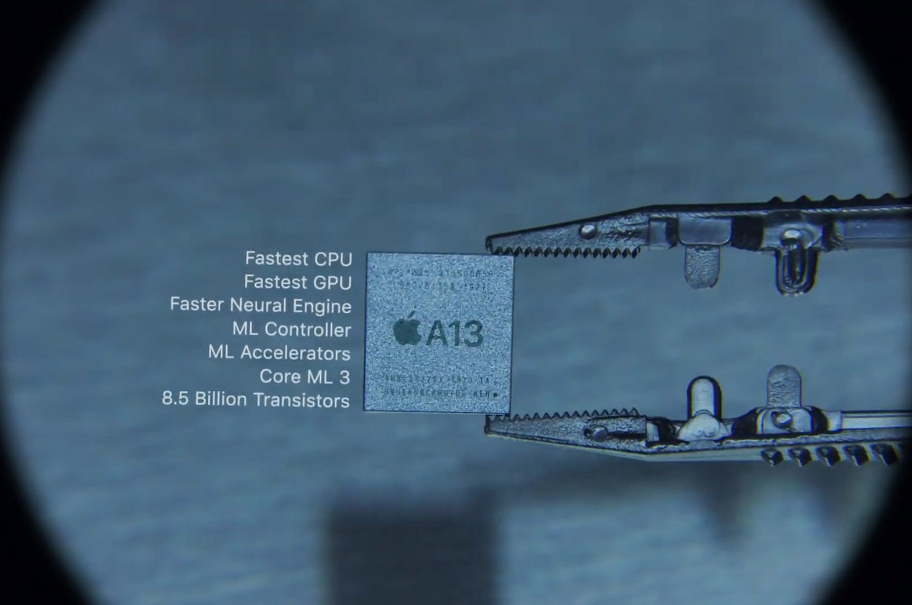

Systema computatrale SoC (SoC) simile est caeliscalpio, ubi omnes moduli functionales designantur et in eundem microplaculum physicum integrantur. Ratio principalis Systematis Computatralis (SoC) est omnes partes principales systematis electronici, inter quas processor (CPU), memoria, moduli communicationis, circuitus analogi, interfaces sensorum, et varia alia moduli functionalia, in unum microplaculum integrare. Commoda Systematis Computatralis SoC in alto gradu integrationis et parva magnitudine consistunt, praebens beneficia significantia in effectu, consumptione energiae, et dimensionibus, ita ut aptissimum sit productis summae efficaciae et energiae sensibilibus. Processores in telephoniis gestabilibus Apple exempla microplaculorum SoC sunt.

Exempli gratia, SoC (Software and Computation) simile est "aedificio magno" in urbe, ubi omnes functiones intus designantur, et varia moduli functionales sunt quasi diversa tabulata: quaedam sunt areae officiorum (processores), quaedam areae oblectationis (memoria), quaedam sunt retia communicationis (interfaces communicationis), omnia in eodem aedificio (microprocessore) concentrata. Hoc permittit totum systema in uno microprocessore silicii operari, maiorem efficientiam et effectum assequendo.

SiP (Systema in Sarcina) - Coniunctio variarum fragmentorum inter se

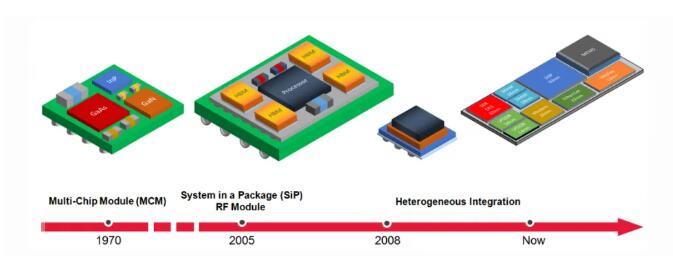

Ratio technologiae SiP differt. Magis similis est pluribus fragmentis cum diversis functionibus intra eundem involucrum physicum includendis. Intendit combinationem plurium fragmentorum functionalium per technologiam involucri potius quam integrationem eorum in unum fragmentum sicut SoC. SiP permittit ut plures fragmenta (processores, memoria, fragmenta RF, etc.) iuxta includantur vel intra eundem modulum congerantur, solutionem systematis formantes.

Conceptus SiP comparari potest cum arca instrumentorum componenda. Arca instrumentorum varia instrumenta, ut cochlearia, malleos, et terebras, continere potest. Quamquam instrumenta separata sunt, omnia in una arca ad commodum usum unita sunt. Huius modi commodum est quod unumquodque instrumentum separatim excogitari et produci potest, et in sarcinam systematis prout opus est "componi" possunt, flexibilitatem et celeritatem praebentes.

2. Characteres Technici et Differentiae inter SoC et SiP

Differentiae Methodorum Integrationis:

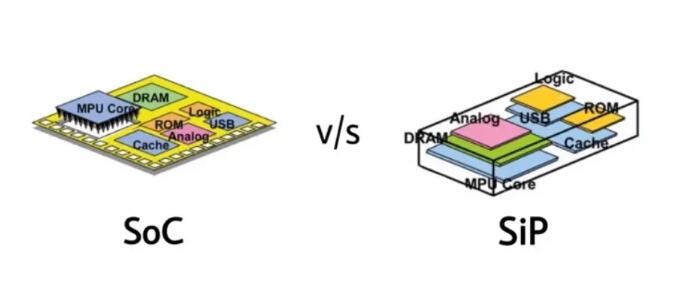

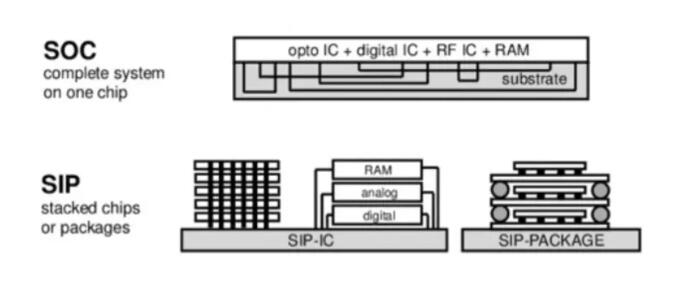

SoC: Moduli functionales diversi (velut CPU, memoria, I/O, etc.) directe in eodem microplaco silicii designantur. Omnes moduli eundem processum fundamentalem et logicam designandi participant, systema integratum formantes.

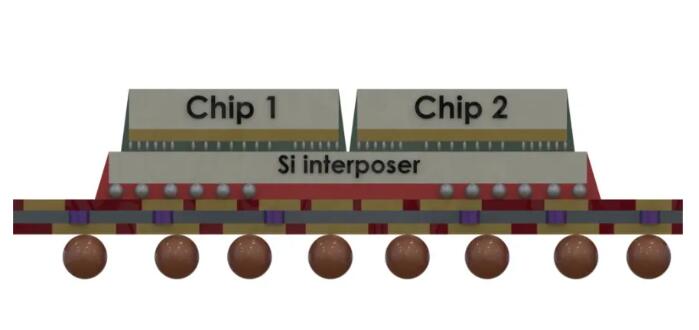

SiP: Diversae laminae functionales per diversos processus fabricari possunt, deinde in uno modulo involucri utens technologia involucri tridimensionali coniungi ad systema physicum formandum.

Complexitas et Flexibilitas Designandi:

SoC: Cum omnes moduli in uno microplaca integrati sint, complexitas designandi maxima est, praesertim pro designatione collaborativa modulorum diversorum, ut digitalium, analogorum, RF, et memoriae. Hoc requirit ut ingeniarii profundas facultates designandi trans dominia habeant. Praeterea, si quaestio designandi cum quolibet modulo in SoC est, totum microplaca fortasse redesignanda erit, quod pericula gravia offert.

SiP: Contra, SiP maiorem flexibilitatem designandi offert. Moduli functionales diversi separatim designari et probari possunt antequam in systema includantur. Si quaestio cum modulo oritur, solus ille modulus substituendus est, ceteris partibus intactis. Hoc etiam celeriores evolutionis celeritates et minora pericula comparatione cum SoC permittit.

Compatibilitas Processuum et Difficultates:

SoC: Integratio functionum variarum, velut digitalium, analogicarum, et RF, in unum microplaculae fragmentum magnopere difficultates in compatibilitate processuum premit. Moduli functionales diversi diversos processus fabricationis requirunt; exempli gratia, circuiti digitales processus celerrimos et parvae potentiae requirunt, dum circuiti analogici accuratiorem moderationem tensionis requirere possunt. Compatibilitatem inter hos diversos processus in eodem microplaculae fragmento assequi difficillimum est.

SiP: Per technologiam involucrorum, SiP potest integrare fragmenta fabricata per diversos processus, solvens problemata compatibilitatis processuum quibus technologia SoC obviam it. SiP permittit ut plures fragmenta heterogenea simul in eodem involucro operentur, sed requisita praecisionis pro technologia involucrorum alta sunt.

Cyclus et Sumptus Investigationis et Evolutionis:

SoC: Cum SoC designationem et verificationem omnium modulorum ab initio requirat, cyclus designationis longior est. Quisque modulus designationem, verificationem et probationem rigorosam subire debet, et totus processus evolutionis aliquot annos durare potest, quod sumptus altos affert. Tamen, semel in productione magna, sumptus unitatis minor est propter integrationem magnam.

SiP: Cyclus investigationis et progressionis (R&D) brevior est pro SiP. Quia SiP directe utitur fragmentis functionalibus iam exstantibus et verificatis ad involucrum, tempus necessarium ad redesignationem modulorum minuit. Hoc permittit celeriores introductiones productorum et significanter imminuit sumptus investigationis et progressionis.

Efficacitas et Magnitudo Systematis:

SoC: Cum omnes moduli in eodem microplaco sint, morae communicationis, iacturae energiae, et impedimenta signorum ad minimum reducuntur, SoC commodum incomparabile in effectu et consumptione energiae praebentes. Magnitudo eius minima est, eam aptissimam reddens applicationibus cum magnis requisitis effectus et energiae, ut telephona gestabilia et microplacae processus imaginum.

SiP: Quamquam gradus integrationis SiP non tam altus est quam SoC, tamen varias laminas compacte includere potest, technologia involucri multi-stratosi utens, unde magnitudo minor est quam solutiones multi-laminae traditionales. Praeterea, cum moduli physice involucri sint potius quam in eadem lamina silicii integrati, quamvis efficacia SoC fortasse non aequet, tamen necessitatibus plurimarum applicationum satisfacere potest.

3. Scenaria Applicationum pro SoC et SiP

Scenaria Applicationum pro SoC:

SoC typice aptum est campis cum magnis requisitis magnitudinis, consumptionis energiae, et effectus. Exempli gratia:

Telephona gestabilia: Processores in telephonis gestabilibus (velut microplagulae seriei A ab Apple vel Snapdragon a Qualcomm) plerumque sunt SoCs valde integrati qui CPU, GPU, unitates processus intellegentiae artificialis, modulos communicationis, etc. incorporant, requirentes et efficaciam potentem et consumptionem energiae parvam.

Processus Imaginum: In cameris digitalibus et dronis, unitates processus imaginum saepe requirunt facultates processus paralleli fortes et latentiam humilem, quas SoC efficaciter assequi potest.

Systema Integrata Altae Perfunctionis: SoC praecipue aptum est parvis machinis cum requisitis strictis efficientiae energiae, ut machinis IoT et rebus indutis.

Scenaria Applicationis pro SiP:

SiP latiorem varietatem condicionum applicationis praebet, aptam campis qui celerem progressionem et integrationem multifunctionalem requirunt, ut puta:

Instrumenta Communicationis: Pro stationibus basicis, itineribus, et cetera, SiP plures processores signorum RF et digitalium integrare potest, cyclum evolutionis producti accelerans.

Instrumenta Electronica Consumptiva: Pro productis sicut horologia gestabilia et auricularia Bluetooth, quae celeres cyclos renovationis habent, technologia SiP celeriores emissiones novorum productorum functionalium permittit.

Electronica Autocinetica: Moduli moderandi et systemata radarica in systematibus autocineticis technologiam SiP ad celeriter integrandos varios modulos functionales uti possunt.

4. Proclivitates Futurae Progressionis SoC et SiP

Inclinationes in Evolutione Systematis Computatralis (SoC):

SoC (Software Assembly) versus integrationem altiorem et integrationem heterogeneam evolvere perget, fortasse maiorem integrationem processorum intellegentiae artificialis, modulorum communicationis 5G, aliarumque functionum implicans, ulteriorem evolutionem machinarum intelligentium impellens.

Inclinationes in Evolutione SiP:

SiP magis magisque innitetur technologias involucri provectas, ut progressus involucri 2.5D et 3D, ut microplagas cum variis processibus et functionibus arcte coniungat, quo celeriter mutantibus postulatis mercatus satisfaciat.

5. Conclusio

Systema computatrale computatrale (SoC) magis simile est aedificationi caeliscalpii magni multifunctionalis, omnes modulos functionales in uno consilio congregans, aptum applicationibus cum requisitis altissimis pro effectu, magnitudine, et consumptione energiae. SiP, contra, simile est "inclusioni" variarum partium functionalium in systema, magis in flexibilitate et evolutione rapida intendens, praesertim aptum electronicis usoribus quae celeres renovationes requirunt. Utrumque sua habet vim: SoC optimam systematis functionem et optimizationem magnitudinis, dum SiP flexibilitatem systematis et optimizationem cycli evolutionis illustrat.

Tempus publicationis: Oct-28-2024